Logisim预习笔记

一些Logisim元件的用法

1.splitter

Fan out:确定输出的分离份数或输入的份数

Bit Width In:输入的数据长度

Bit n:对输出位数的位置分配

2.Bit Extender

Bit Width In:输入的数据长度

Bit Width Out:输出的数据长度(即扩展到多少位)

Extension Type:扩展方式选择:

zero补0

one补1

sign补原数据符号位

input根据上方输入选择补充0或1

3.And,Or,Nand,Nor,Xor,Xnor

| a | b | and | or | nand | nor | xor | xnor |

|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 1 | 1 | 0 | 1 |

| 0 | 1 | 0 | 1 | 1 | 0 | 1 | 0 |

| 1 | 0 | 0 | 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 | 0 | 0 | 0 | 1 |

- and的表达式是AB,or的表达式是A+B

- xor门当输入数据超过2时,对应位为1的数量超过1时其异或结果即为0

4.Odd Parity(奇校验)

Data Bits:输入数据的长度设置(下同)

Numbers Of Inputs:输入数据个数的设置

Output Value:通过检验和没通过检验分别输出数据类型

奇校验门输入数据同一位有奇数个1就输出1,和Xor门有差别

5.Controlled Buffer

当控制输入引脚输入为0或浮动时,输出数据也是浮动的

当控制输入引脚输入为1时,输出数据即为输入数据(缓冲器作用)

当控制输入引脚输入错误,输出数据也是错误

Controlled Inverter相当于Controlled Buffer+not

6.Multiplexer

Select Bits:选择端输入数据长度设置,若其长度为n,则输入数据个数为2^n

Include Enable:若选择,在元件下部右侧出现使能输入,当输入为1时元件才可用(默认1)

解复用器Demultiplexer和mux类似(功能相反),注意其下侧左侧为使能,右侧为选择输入

7.Decoder

Select Bits同上,差别为此元件无输入,和Select Bits输入数据对应的端口(例如输入110就是6号端口输出1)

Three State选择:可以决定没被选择的端口输出0还是浮动值

与Dex相同,下侧左端为使能输入,右端为选择输入

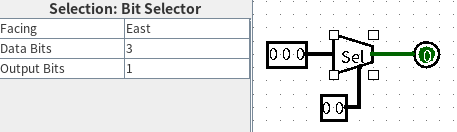

8.Bit Selector

其原理是对输入数据进行分段和选择输出,例如输入端长度设定为8,输入为110101001,输出端长度为3,则相当于要将输入端以三位为一组分开,此时选择段输入长度即为2(因为第0,1,2组都有值),若选择段输入0,相当于取第0组,即输出001(从低位开始排序),以此类推,如果输入10取第2组,则需要在最高位补0,故输出011,第三组完全没有值,则输出000

- 因此本元件的分组大小和选择段输入长度都由输入输出长度确定

9.Adder,Subtractor,Multiplier,Divider

加减乘除元件大体类似,都是以西北侧输入为第一个数,西南侧输入为第二个数,结果从东侧输出

加法北侧可以输入要加入总和的进位值,南侧可以输出计算完成后的进位位

减法北侧可以标记借位,如果输入1表示借1,南侧可以输出符号,如果得到负数,则输出1,否则输出0

乘法北侧也表示进位值,东侧输出的是符合输出长度的低位,而南侧输出的是结果中没有被完全输出的高位值

除法北侧表示被除数的高位(即西北侧输入的数的高位),东侧输出的是符合输出长度的商低位,南侧输出的是余数

10.Negator(-x)

- 取反加一,输出补码

11.Comparator

Numeric Type:输入的两个数据的类型,二进制补码或者无符号数

输入以西北侧输入为a,西南侧输入为b,当a>b时东北侧输出1,a=b时正东侧输出1,a<b时东南侧输出1

比较原理是从每个数字的最有效位开始并行向下比较,直到找到不同值位置,如果遇到错误值或浮点值,那么输出也匹配错误值和浮点值

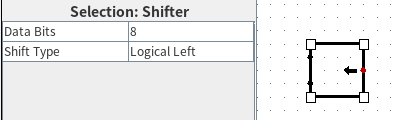

12.Shifter

西北侧输入为需要被移位的数据data,西南侧输入为移位多少的数据dist,两者的关系是dist=[log2data]+1,这样才能满足可以把所有数据位都移走的上限

shift Type:移位规则,分为:

逻辑左移:所有数据左移dist位,低位用0填充(被移除数据范围的位数丢弃,下同)

逻辑右移:所有数据右移dist位,高位用0填充

算术右移:所有数据右移dist位,高位用原数据最高位填充

循环左移:所有数据左移dist位,被移出数据范围的位循环进入低位

循环右移:所有数据右移dist位,被移除数据范围的位循环进入高位

13.Register(寄存器)

其功能为将输入值实时存储在寄存器中,在时钟上升沿将储存在寄存器中的数据传输给输出

正西侧为输入,西南侧为使能输入,南侧左端为时钟输入信号,右端为复位信号,东侧输出

使能在没有输入时默认为1

复位信号是异步重置,相当于其只要为1就让寄存器的值重置为0,和时钟上升沿无关

14.Counter

计数器持有单个值,每次时钟到达上升沿触发计数器,其会根据左侧输入更新值并且更新输出

西北侧和西南侧输入分别为load和count,南侧的时钟和reset和register相同,正东侧为输出,东南侧为carry(进位)输出,当计数器中值最大但仍对其指示加一或值最小但仍指示减一时即变为1

计数器存储数字的更新方式(增加减少都是随时钟上沿增加减少1)

load count 触发情况 0或x 0 值不变 0或x 1或x 值增加 1 0 载入输入值 1 1或x 值减少 - Action On Overflow:当存入数据溢出时的处理方式

Wrap around重新计数:递增则回0,递减则回最大值

Stay at value保持前值:递增时保持最大值,递减时保持0

Countinue counting继续计数:计数器继续递增、递减,保持数据位计数

Load next value加载下一个值:下一个值直接从输入中获取

15.RAM

使用分离的加载和存储端口模式,即将数据接口选择”Seperate load and store ports”

西侧A接口表示要操作的数据的地址,D接口表示要存入RAM的数据

南侧左边小三角形输入时钟信号,右侧ld接口输入选择信号(1bit)为0时储存数据,为1时读取数据

东侧D接口输出显示当前正在存储/读取的数据

其余引脚:str输入引脚,当其为1或浮动时才能将左侧D数据存储到RAM中

其余引脚:sel输入引脚,根据其为1,0或浮动决定启动或者禁用整个RAM

其余引脚:clr输入引脚,当值为1时RAM所有储存值固定为0(clear)

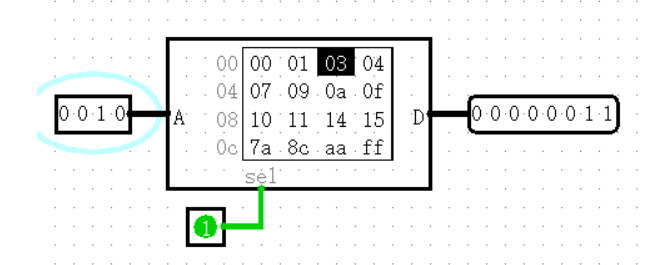

16.ROM

和RAM比较类似,但是是只读存储器(无法修改)

左侧A接口表示想要读取的数据地址,右侧D输出读取的数据

南侧sel引脚输入值为1时才能正常读取,当输入值为0时就无法读取,D输出为浮动值

改变其存储内容的方式有:利用右键手动输入存储值,或者导入txt文件。如果想要导入txt文件(例如MARS输出的)需要在文件第一行写”v2.0 raw”字样才能正常读入。

(其余元件用到再补充)

Logisim和组合电路

利用logisim构成组合电路的问题是,难以直接从真值表转化为logisim的电路图,此时需要利用布尔表达式来进行传递,先将真值表变为布尔表达式,再将表达式用电路的与或非门表示。

(但是可以从电路图直接转化为真值表,只需要一个一个带入0,1值即可)

真值表向表达式的转化可以有两种方法完成:

eg.(c为输出)

| a | b | c |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

1.积项求和和和项求积(相当于离散数学中的主析取范式和主合取范式)

- 积项求和:输出为1的行产生积项(and),然后将所有项求和(or),注意要将所有为0的变量取反,则此处c=((

a)b+a(b)) - 和项求积:输出为0的行产生和项,然后将所有项求积,其余同上,则此处为c=(

a+b)(a+b)

2.卡诺图

- 将输入信号尽可能均匀的分为两组(一组n个一组m个),然后构造一个2^n * 2^m的矩阵,注意相邻的两个组合只有一个信号的值有变化

将真值表填入卡诺图

相邻的邻居如果都为1,则可以进行化简,但是邻居个数必须是2的整数幂

组越大最终表达式越简单,则应该尽可能选择尽可能大的单元,避免单个单元

注意四角的单元,因为其相当于和另一端的单元相邻

卡诺图是更加好的选择,因为卡诺图不仅可以求出表达式,还可以化简,让电路图更加精简

在logisim中可以利用window>Combinational Analysis,自己定义输入输出并输入真值表或者计算公式,logisim就可以自动构建组合电路,还可以选择保证所有门元件都只有两个输入,或者只适用Nand门。

Logisim和时序电路

双稳态电路:由两个反相器构成双稳态,该电路的输出取决于电路的初始状态,当初始Q为0时,Q永远为0,当初始Q为1时,Q永远为1。因此其已经可以保存1位信息了,但是缺乏实用价值。

- 此处已经可以看出,我们可以利用门等运算器的逻辑关系,利用组合电路构建出拥有储存性质的电路,将其进行拓展即可得到时序电路

RS锁存器:其结构如下图。首先分析当R=1或S=1的这些情况,因为此时N1,N2的nor门明显输出为0,因此这三种状态和之前的输出Qprev无关。

- 再考虑R=S=0时,则新的输出Q和之前的输出Qprev有关,此时若Qprev为0,则Q为0,Qprev为1,则Q为1。我们可以发现Q的输出在这种情况下完全取决于Qprev并和Qprev完全相同。

- 因此我们可以手动利用RS储存器存入0或1,方法就是先利用R/S取值为0/1或1/0时给Q赋一个初值,比如如果想给Q赋值1,则R/S赋值为0/1。然后再将R和S变成0,相当于切断了外界对这个锁存器储存值的影响,此时Qprev为1且R=S=0,则Q值恒为1。

- RS锁存器中R输入即为Reset,而S输入为Set的意思。因为当S=1,R=0时给Q置1(称为置位)S=0/R=1的状态给Q置0(称为清零)S=R=0时称为保持状态,因为Q只和前状态Qprev相关。

- RS锁存器中S=R=1是非法状态,不应被调至此种状态。

- RS锁存器的局限是不具备时间特性,无法被时钟信号控制。

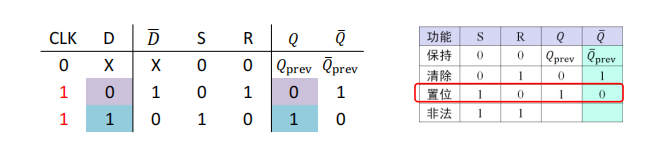

D锁存器:输入包括CLK(时钟信号)和D信号

- D锁存器是RS锁存器的扩展,其中使用了一个RS锁存器模块,结构见下图:

- 分析方法:当CLK信号为0时,无论D信号,进入RS锁存器的信号R和S都一定为0,此时RS锁存器的状态一定为保持(R=S=0)

- 当CLK信号为1时考虑D信号,当D为0时R=1,S=0,此时Q为0,当D=1时R=0,S=1,此时Q为1,相当于D值可以选择置位或者清除操作,并且这种结构可以保证不会出现R=S=1的非法状态。

- 因此D锁存器已经有了很明显的时间概念,CLK输入决定何时进行保存(为1传输D值,为0保持Qprev),D输入决定保存什么值。

- 局限在于,在高电平(CLK为1)时Q值对D值敏感,会随时随D值翻转(这种特性被称作电平缓冲器),则没有完全达到对时钟的设计初衷。

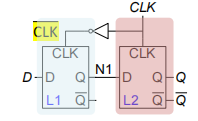

D寄存器:利用两个D锁存器串联,并且两个锁存器的CLK输入反相。

先研究CLK:当CLK为0时L1可以透传而L2保持,相当于将D传送到N1;当CLK为1时L2可以透传而L1保持,则相当于把确认为稳定值的D(N1)传送到Q。

则相当于,在CLK由0变1时将D透传到Q,因为CLK为0时Q不变,同时保证CLK为1时D不变,因此Q的值就是CLK由0变1时传入的D值。

- 其优点在于,实现了边沿处(时钟上升沿)保存数据,而确保D在非时钟上升沿的任何变化都不会影响Q。这种特性被称为边沿触发。

- D寄存器时间特性:

建立时间:CLK边沿前D保持稳定的时间TS

保持时间:CLK边沿后D保持稳定的时间TH

输出延迟:CLK边沿后Q输出有效值的时间TQ - D值能否被保存取决于TS,TH,而Q值何时能被看到取决于TQ

Logisim中和时序相关的功能:

- Tick Once 时钟高低平变化一次(ctrl+T)

- Ticks Enabled 允许时钟开始工作(高低平反复变化)(ctrl+K)

- Tick Frequency 调节时钟变化频率

- Reset Simulation 回到初始状态(ctrl+R)

Logisim和有限状态机

有限状态机

- 定义:表示有限个状态以及这些状态之间的转移和动作等行为的离散数学模型

- ”状态“:电路所处的特定工作阶段,每一个状态需要给予一个编码值,然后将一个寄存器作为状态的寄存器(输出的编码值就是状态),其中存储的状态取决于次态逻辑的输出(寄存器的输入)

- 次态逻辑:根据当前状态和输入,计算下一个状态(的编码值),是一种组合逻辑

- 输出逻辑:根据输入和状态计算输出值

- 状态机表示方法:状态机,状态表

状态机开发步骤:

1.规划状态总数,确保所有状态都被包括

2.构造状态图,必须让所有的状态转移条件都是完备的,保证状态转移能够进行

3.根据输入信号,当前状态,下个状态构造寄存器输入信号门电路(真值表推演)(次态逻辑)

4.根据设计选择当前状态的输出值(输出逻辑)状态机核心:用次态逻辑计算下一个时钟周期寄存器的输入

设计要点:需要给状态机设计一个初始状态,这样在开始的时候有一个确定的状态。同时需要有一个复位信号将状态机转化为初始状态。

不同类型状态机:

Moore型状态机:输出信号只由当前状态决定,和输入信号无关

Meely型状态机:输出信号由当前状态和输入信号共同决定状态机构建例子:

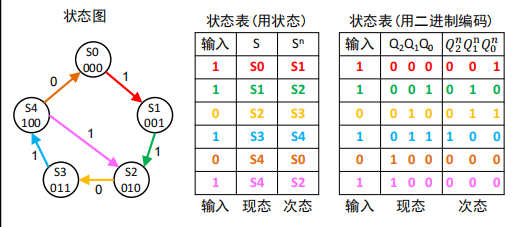

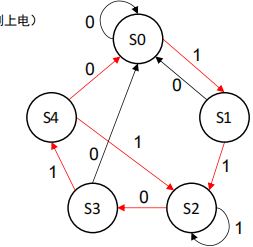

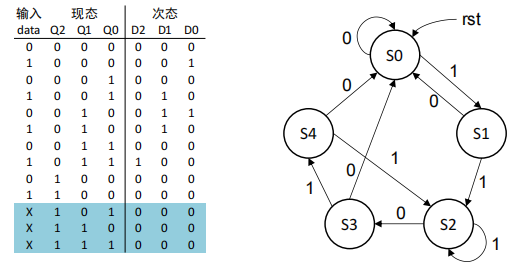

序列检测器的1位串行输入与时钟严格同步。当检测器连续收到串行码{1101}后,检测标志输出1且持续时间为1个cycle,否则输出0。构建序列检测机。1.构建状态

由于一个收到串行码的过程需要四个时间周期(分别输入1101),则可以将其分为四个状态:1(S1)、11(S2)、110(S3)、1101(S4),最后再添加一个没有匹配成功需要从头开始的状态(S0)。2.根据状态和题意给出状态转移情况

- 3.增加复位信号Reset,即如果输入信号是复位信号的话,状态变回S0

- 4.构造门电路,创建次态逻辑:普适方法为把每个状态转移转化为一行真值表,再转化为表达式和门电路。(可靠性设计:所有的未定义状态转化为初态)

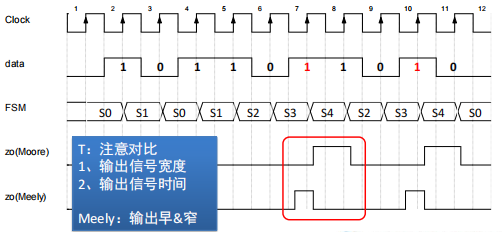

5.产生输出信号(输出逻辑):本题的条件是”检测标志输出1且持续时间为1个cycle,否则输出0“,有两种输出逻辑(本质是选择哪一种类型的状态机)

如果理解是状态是S3(110)并且检测到输入为1,就直接输出1,则为Meely型

如果理解是状态是S4(1101)才输出1,则为Moore型

由于本题S3或S4都只持续一个cycle,因此不用考虑状态持续问题对比两种类型状态机输出:Moore型输出晚,有效时间只和状态相关,以cycle为单位

Meely型输出提前(因为考虑输入),但是有效时间不止考虑状态,也考虑输入

- 利用Logisim构建状态机的一般方法:将状态机分成三个模块:状态转移模块(构建次态逻辑),状态存储模块(存储当前状态)以及输出模块(构建输出逻辑),最终将三个模块结合即可。(Moore和Meely的差别是输入数据是否同时输入给次态逻辑和输出逻辑,如果是就是Meely型,否则是Moore型)

(此图为Meely型)